# An Improved Voltage Level Balancing Method for Nine Level Diode Clamped Inverter

# S Narmadha

Master of Engineering, Department of EEE, Gnanamani college of Engineering, Namakkal, Tamil Nadu, India.

# S. Venketasen

Lecturer, Department of EEE, Gnanamani college of Engineering, Namakkal, Tamil Nadu, India.

Abstract - In this project active front-end solution to balance dc-link capacitor voltage of nine-level diode-clamped inverter. Capacitor voltage balancing performed by three-level boost converter (TLBC) connected to the two inner capacitors of ninelevel diode-clamped inverter and additional balancing circuits at other two outer capacitors. Proposed configuration tested through simulation and experiment for various load power factor conditions at high modulation index. The result demonstrates the reliability of proposed configuration to balance the dc-link capacitors voltage at desired level. The TLBC has advantages in high power applications to reduced switching losses and reduced reverse recovery losses of the diode. A fuzzy control system is a control system based on fuzzy logic a mathematical system that analyzes analog input values in terms of logical variables that take on continuous values between 0 and 1, in contrast to classical or digital logic, which operates on discrete values of either 1 or 0 (true or false, respectively). The more level can be produce, it does will be much better for the application. It is because the value of THD also will decrease once the levels of the multilevel inverter increase.

# Index Terms – DC-link capacitor voltage balancing, diode clamped, multilevel inverter, three-level boost converter (TLBC).

#### 1. INTRODUCTION

IN response to the growing demand for high power inverter units, multilevel inverters have been attracting growing attention from academia as well as industry in the recent decade. Among the best known topologies are the H-bridge cascade inverter, the capacitor clamping inverter (imprecated cells), and the diode clamping inverter. for the diode-clamped inverter with more than three levels, a passive front-end capacitor voltage balancing method is only achievable if the modulation index is limited to about 60% of its maximum value for loads with a typical 0.8powerfactor. If the modulation index is increased more than this value, the center capacitors gradually discharge, and finally, the inverter output converges at three levels. To overcome this limitation, a multilevel inverter can be supplied by isolated dc sources such as external circuit as the active front-end solution of dc-link capacitor balancing using balancing circuit by transferring charge from one capacitor to another capacitor to equilibrium level or the modification of the pulse width.

The capacitor clamping inverter, though the three-level scheme of which was published in the early 1980's, had been rarely discussed until the introduction of the "imbricated cells". The individual clamping capacitor needs only to smooth the switching frequency ripple voltage and the required capacity for each clamping capacitor is therefore small. However, as the number of level increases, such problems as thermal designing, low-inductance designing, as well as insulation designing of the system will become critical. Medium voltage drives using four-level capacitor clamping inverter has recently been available on the market.

## 2. SYSTEM MODEL

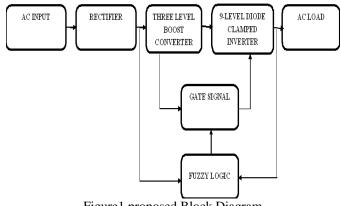

AC input is given to the rectifier and then the rectifier converts the ac signal to the dc then the output is given to the three level boost converters, its boost up the output of the rectifier and rectifier output is given to the fuzzy logic. The fuzzy logic tuning the output the three level boost converter gives its signal to the gate signal. The three level boost converters gives its output voltage to the nine level diode clamped inverter to increase the level of the voltage, and also gate signal output is given to the nine level diode clamped inverter. The nine level output is given to the fuzzy logic. The nine level diode clamped inverter inverts the dc into the AC then it given to the AC load.

Figure1 proposed Block Diagram

The inverter is used to control the fundamental voltage magnitude and the frequency of the ac output voltage.AC loads may require constant or adjustable voltage at their input terminal, when such loads are fed by inverters, it is essential that the output voltage of the inverters is so controlled as to full fill the requirement of the loads. For example if the inverter supplies power to a magnetic circuit, such as a induction motor, the voltage to frequency ratio at the inverter output terminals must be kept constant. This avoids saturation in the magnetic circuit of the device fed by the inverter.

# 3. DIODE CLAMPED INVERTER

The first invention in multilevel converters was the so-called neutral point clamped inverter. It was initially proposed as a three level inverter. It has been shown that the principle of diode clamping can extended to any level.

As the name of the diode clamping inverter implies, any main switch in the string at blocking state must be clamped to a corresponding dc link capacitor via relevant clamping diodes.

By which, blocking voltage of the main switch will be constrained to the nominal value. This mechanism in the proposed diode clamping inverter will be discussed below.

In cell are always ON, while and are always OFF, and work alternatively connecting the inverter output to and respectively. Obviously, is directly clamped to by after it's turn-off, while in series with and is indirectly clamped to by and after its turnoff. Further, in series with and is indirectly clamped to by and ; in series with is indirectly clamped to by and , while is directly clamped to by . Suppose that for cell and each blocks voltage, and each blocks zero voltage. Then, and are all clamped to at when OFF.

Indirect clamping and the subsequent unequal blocking voltage distribution problem holds also for and and , and , together with their relevant clamping diodes in cell (b), cell (c) and cell (d). Due to the fact that the stray capacitance of the neighboring outer switch experiences one more discharging than the inner switch, among the blocking devices, the outer switch will always block less voltage while the inner device will always block more voltage The center device will always be exposed to the highest voltage stress. network for the new diode clamping inverter. Unequal blocking voltage distribution problem arising from indirect clamping exists also with the conventional diode clamping inverter as mentioned in Section I. The severity of this problem is dependent on the stray inductances of the structure. With refined bus-bar designing technique, and in particular, appropriate positioning of an auxiliary clamping, the problem will be mitigated. resistive auxilary clamping.

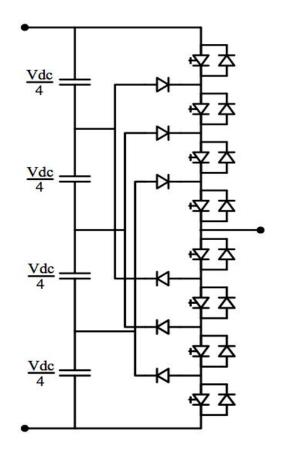

An m-level diode clamped converter typically consists of m-1 capacitors on the dc bus and which produces m levels of phase

voltage. The diode clamped converter produces (m-1)/2 levels above and below the zero level.

Figure 2 Diode Clamped Leg Circuit

If one assumes that the rating of the diodes is much more the same as the rating of the main switches in the converter, a problem will arises with the diode clamped converter and the number of diodes required in the circuit will increases with the number of levels. Let us consider that the switch chain from the positive top rail, to the output connection. Having half of the total number switches exist either in the top or bottom half of the switch chain as this will corresponds to m-1 switches. If one has a chain of m-1 switches then there will be m-2 connections in between the switches. The diode chains are being connected to all these connections points. Each of these diode chains will stop on a switch junction point in the bottom half of the inverter totem pole. Each diode chain has to bear the total capacitor voltage such as assuming that the diode voltage rating is the same as the switch rating then this would mean that each diode chain has to consist of m-1 diodes. As a result the total number of diode is:

Number of diodes = (m-1) (m-2)

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 4, Issue 3, March (2016) www.ijeter.everscience.org

Let's refer to Figure which is a three level diode clamped converter. In this circuit, the dc bus voltage is being split into three levels by two series connected bulk capacitors, C1 and C2. The middle point of the two capacitors n can be defined as the neutral point. The clamping diodes' function in the circuit is to prevent the voltage across one of the switching devices which surpass the voltage across one of the capacitors. The output voltage Van has three states which are: Vdc/2, 0, and – Vdc/2. For voltage level Vdc/2 switches S1 and S2 need to be turned on; for –Vdc/2 switches S1' and S2' need to be turned on; and for the 0 level, S2 and S1' need to be turn on.

#### 4. FUZZY LOGIC ALGORITHM

Today control systems are usually described by mathematical models that follow the laws of physics, stochastic models or models which have emerged from mathematical logic. A general difficulty of such constructed model is how to move from a given problem to a proper mathematical model. Undoubtedly, today's advanced computer technology makes it possible; however managing such systems is still too complex.

These complex systems can be simplified by employing a tolerance margin for a reasonable amount of imprecision, vagueness and uncertainty during the modelling phase. As an outcome, not completely perfect system comes to existence; nevertheless in most of the cases it is capable of solving the problem in appropriate way.

Even missing input information has already turned out to be satisfactory in knowledge-based systems. Fuzzy logic allows to lower complexity by allowing the use of imperfect information in sensible way.

#### 5. RESULT AND DISCUSSION

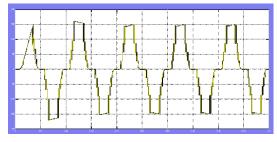

Figure 3 Nine level output waveform

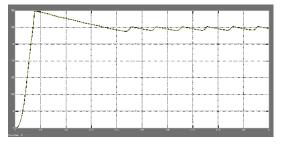

Figure 4 Output voltage waveform

#### 6. CONCLUSION

In this Project new configuration to balance dc-link capacitor voltages of nine-level diode-clamped inverter. Connecting a boost-three level converter (TLBC) at the input of the inverter regulates the two inner dc-link capacitors voltage at desired level with changing of converter DC source and at the same time provides voltage balancing. Balancing circuits are added to balance voltage of the two outer capacitors. Overall, the investigations show that the proposed converter operates well in various load power factor conditions. This configuration is suitable for grid-connected DC system due to unidirectional power transfer.

### REFERENCES

- Nabae, I. Takahashi, and H. Akagi, "A New Neutral-Point- Clamped PWM Inverter," *IEEE Transactions on Industry Applications*, vol. IA-17, no. 5 pp. 518-523, 1981.

- [2] C. Hochgraf, R. Lasseter, D. Divan, and T. A. Lipo, "Comparison of multilevel inverters for static VAr compensation," in *Conference Record* of the IEEE Industry Applications Society Annual Meeting, 1994, pp. 921-928 vol.2.

- [3] M. Marchesoni and M. Mazzucchelli, "Multilevel converters for high power AC drives: a review," in *Proc. IEEE International Symposium on Industrial Electronics*, 1993, pp. 38-43.

- [4] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 7 pp. 2219-2230, 2010.

- [5] B. A. Welchko, "A Three-Level MOSFET Inverter for Low-Power Drives," *IEEE Transactions On Industrial Electronics*, vol. 51, no. 3 pp. 669-675, June 2004.

- [6] A. Bendre, S. Krstic, J. Vander Meer, and G. Venkataramanan, "Comparative evaluation of modulation algorithms for neutralpointclamped converters

- [7] N. Hatti, Y. Kondo, and H. Akagi, "Five-Level Diode-Clamped PWM Converters," *IEEE Transactions on Industry Applications*,

- [8] N. Hatti, K. Hasegawa, and H. Akagi, "A 6.6-kV Transformer less Motor Drive Using a Five-Level Diode-Clamped PWM" IEEE Transactions on

- [9] M. M. Renge and H. M. Suryawanshi, "Five-Level Diode Clamped Inverter to EliminateCommon Mode Rating Induction Motor Drives," *IEEE Transactions on Power Electronics*, vol. 23, no. 4 pp. 1598-1607, 2008.